# An Efficient plan of QCA Full-Adder and Subtractor by LowPower Dissipation

<sup>1</sup>A.R. Aravind ,<sup>2</sup> Nirmala.D , <sup>3</sup>T.Punitha

<sup>1,2</sup>Assistant Professor, Department of Electronics and Communication Engineering,

<sup>1</sup>Prince Shri Venkateshwara Padmavathy Engineering College, Chennai

<sup>2</sup>Prince Dr.K.Vasudevan College of Engineering & Technology, Chennai.

<sup>3</sup>Faculty, Prince Shri Venkateshwara Arts and Science College, Gowriwakkam.

#### **Abstract**

The continuous market demands for high performance and energy-efficient computing systems have steered the computational paradigm and technologies towards nanoscale quantum-dot cellular automata (QCA). In this paper, novel energy- and area- efficient QCA-based adder/subtractor designs have been proposed. First, a QCA-based 3-input XOR gate is designed and then a full adder and a full subtractor are realized. The power consumption of the proposed design was tested via the QCA Pro estimator tool with different kind of energy (c 0.5 Ek, c 1.0 Ek, and c 1.5 Ek) at temperature T 2 in Kelvin. QCA Designer 2.0.03 software was applied to evaluate the simulation results of the proposed designs. The proposed design has better complexity than the conventional designs in terms of cell count, area, and power dissipation.

## 1. Introduction

Over the past few decades, the microelectronics industry has been driven by increasing market demands for enhanced integration, energy efficiency, and speed of integrated circuits (ICs) [1–4]. On one side, traditional Complementary Metal Oxide Semiconductor (CMOS) based transistors cannot be reduced much smaller than their current size, due to current leakage problems arising from quantum mechanically tunneling, so the device cannot be switched off properly and increased heat dissipation, which threatens to melt the chip. This fact has pushed designers to search for new technologies to allow greater integration and lower power consumption for Digital Signal Processor (DSP) IC applications. On the other side, scalability of the classical technology is reaching the end that makes the development of monomolecular instruments. International Technology Roadmap for Semiconductors (ITRS) summarizes several new nanodevices that can replace CMOS, such as single- electron transistor (SET), resonant tunneling diode (RTD), carbon annotates (CNT), and quantum-dot cellular automata (QCA) [5]. Quantum-dot cellular automata (QCA) is one of the most promising solutions to design

Ultralow power and very-high-speed digital circuits, which can be scaled down to the molecular nanoscale device level [6]. It is an up-and-coming nanotechnology with strong prospects to supplement and possibly replace the current CMOS technology [7–9]. Unlike conventional CMOS structures, QCA-based structures represent binary values based on the positions of conned electrons in certain quantum dots. This ultimately allows the QCA-based structure to surpass CMOS-based counterparts in terms of switching speed, device density, and power consumption.

Essentially, QCA offers potential advantages of ultralow power dissipation. QCA is expected to achieve very high device density of 1012 device/cm<sup>2</sup> and switching speeds of 10 ps and a power dissipation of 100 W/cm<sup>2</sup> [10]. In QCA technology, no voltage or current is used. It is based on Coulombic interactions of electrons in the quantum dots. Therefore, it will be the alternative

ISSN NO: 2394-2886

candidate for CMOS technology currently used in integrated circuits (ICs). The main concern of this paper is to present a new design of 1-bit full adder and 1-bit full subtractor based on QCA technology, which yields significant reduction in terms of cell count, area, and energy dissipation.

## 2. Background of QCA Technology

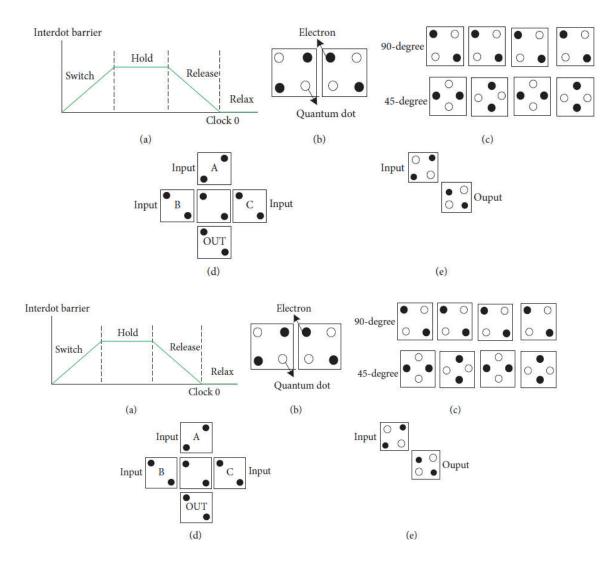

Typically, QCA devices are described on the basis of sym- metric square cells, whereby all computational logic gates and memory structures can be correctly imitated. These structures can be implemented by assembling QCA cells in a The QCA cell has four quantum dots and two electrons [7]. Two electrons tend to occupy diagonal quantum dots owing to the Coulomb force, forming two configurations for encoding binary logical "0" and "1" as depicted in Figure 1(b). The majority and the inverter gates are two fundamental gates of QCA technology used for the circuit design as shown in Figures 1(d) and 1(e), respectively. The inverter can inverse the polarization state of an input cell by arranging two cells diagonally. The three-input majority gate is a core logic device of QCA [6–10]. In addition, the QCA majority voter gate contains five cells forming a cross with a cell in the center as a device cell, three cells as its inputs, and one cell as its output. The device cell polarity is determined based on Coulomb repulsion of the three inputs

Traditional CMOS circuits, which rely on currents to process information, the calculation of QCA circuits relies entirely on the Coulomb force between electrons, which is fast and disordered. In this area, the clocking mechanism provides energy for QCA circuits to make up for the loss in dissipative processes due to switching the state of polarization. In this context, energy is provided by an external electric or magnetic field. Generally, clocking has four phases, which are Switching, Hold, Release, and Relax, as illustrated in Figure 1(a). In QCA, four clock signals are used, where a clock has a phase deference of 90 degrees rather than the next and the previous signals. For example, when Clock0 is in the Hold phase, Clock1 is in the Switching phase and datatransmission is performed from Clock0 cells to Clock1 cells[9, 10].

## 3. Proposed Designs

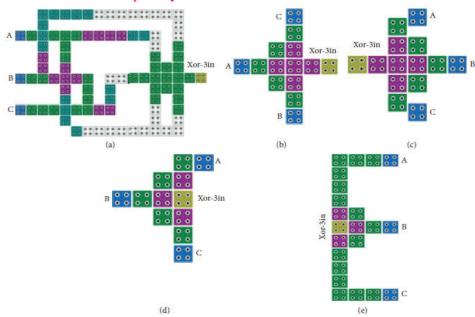

In this section, a novel 3-input XOR gate with excellent performance indicators has been proposed. Thereafter, an optimum full adder and a full subtractor are provided via the proposed gate. The Proposed Three-Input QCAXOR Gate. The XOR gate is the essential component of many digital circuits, such as parity bit generator circuit and arithmetic circuits. Up to date, various models of XOR gates have been reported in the literature [8]. Figure 2 shows some previously designed exclusive-OR gates. In 2014, Angizi et al. [10] presented an XOR gate based on QCA technology. This circuit consists of 94 cells and occupied 0.073 μm2 area with a delay of 1.5 clock cycles. In 2016, another three-input XOR gate was introduced by Ahmad et al. [11]. As can be seen, this design consists of 14 cells with an area of 0.022 μm2. So, output appears after 0.5 clock cycle. In 2017, Bahar et al. [2] presented another XOR gate whose layout realization is shown in Figure 2(e). As shown in Figure 2(e), this design consists of 12 cells with an area of 0.012 μm2. In this work, we first designed a novel 3-input XOR gate; then a new QCA full subtractor and a full adder are suggested using this circuit.

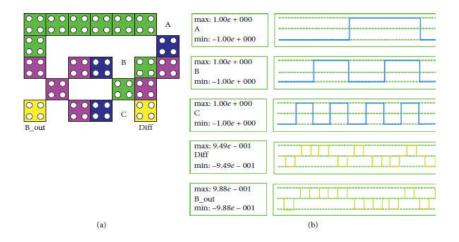

Proposed Full Adder and Full Subtractor Designs. Previous related investigations about full adder and sub-tractor have been implemented widely on QCA technology. These performance indicators about full adder and full subtractor are considered: excellent power consumption, smaller delay, and lower complexity. Here, the proposed 3- input XOR gate is used to obtain

both an efficient design of full adder and full subtractor in terms of latency, area, delay, and power consumption. The proposed designs are verified by simulating them with QCA Designer software

Figure 1: (a) four-phase clocking scheme. (b) Logical states defined by the electron configuration for the QCA cell consisting of four quantum dots, (c) A binary wire that can be achieved by two cell layouts. (d) Majority gate with three inputs and the single output with a binary state decided by majority voting behavior, (e) Inverter that is achieved by placing the two cells diagonally.

Figure 2: Previous three-input XOR gate based on QCA technology. (a) [20], (b) [21], (c) [22], (d) [23], and (e) [24].

## 4. Results and Discussions

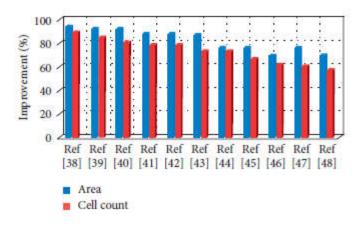

Reduction in the adder/subtractor size will lead to a sub- sequent reduction of the scaled-up systems. In this section, a comparison is made between the proposed QCA 3-input XOR gate and the previous ones. Besides, a comparison is made between the proposed QCA full subtractor and previous works, and, finally; we present a comparison between the proposed QCA full adder and similar previous schemes. Here, the advantage of the QCA circuits implemented in this manuscript is evident. As can be seen from Table 3, the suggested XOR gate has a significant advantage over all. In fact, the area has improved at least 45.4% and cell count at least 42.8%. On the other hand, the proposed full adder and full subtractor have already been designed and simulated using QCA Designer; compared with conventional schemes, the numbers of cells consumed are reduced by 58.69% and 37.5%, respectively. The designs reported in this paper are superior in terms of important parameters

Figure 3: (a) layout of the proposed full adder and (b) its simulation results.

Figure 4: Improvements of proposed adder over others.

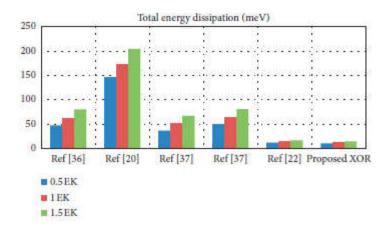

Figure 5: total energy dissipation of the adders at three different tunneling energy levels.

The results associated with the power consumption analysis of the proposed XOR gate and the previously re- ported designs. The energy dissipation comparisons of the XOR gates listed in Table 4 are depicted in bar-graph forms as shown in Figure 4. It can be seen from Figure 4 that the proposed gate consumes the lowest amount of energy over previous designs, and therefore it is very appropriate for ultralow power devices. The thermal layout of proposed 3-input XOR gate is shown in Figure 5.

## Conclusion

Design of low-power high-speed adder/subtractor is always a challenge for DSP applications. In this article, a novel design of 3-input XOR gate, 1-bit full adder, and 1-bit full subtractor in the QCA technology has been presented. The QCA Designer 2.0.3 simulation tool was used to verify the functional correctness of the proposed structures and assess their structural cost in terms of the occupied area. By comparison of previous designs and the proposed designs, it could be concluded that the proposed design has appropriate features and performance. In the future, we will strive to explore and construct more excellent full adder/full sub-tractor unit architecture in order to provide basic module for the larger-scale arithmetic operation circuits on QCAplatform.

- 1. R. H. Dennard, F. H. Gaensslen, H.-N. Yu, V. Leo Rideovt, E. Bassous, and A. R. Leblanc, "Design of ion-implanted MOSFET's with very small physical dimensions," IEEE Solid- State Circuits Newsletter, vol. 12, no. 1, pp. 38–50, 2007.

- 2. K. Bernstein, R. K. Cavin, W. Porod, A. Seabaugh, and J. Welser, "Device and architecture outlook for beyond CMOS switches," Proceedings of the IEEE, vol. 98, no. 12, pp. 2169–2184, 2010.

- 3. N. Z. Haron and S. Hamdioui, "Why is CMOS scaling coming to an END?" in Design and Test Workshop (IDT), pp. 98–103, 3rd IEEE International, Tampere, Finland, 2008.

- 4. International Technology Roadmap for Semiconductors, Process Integration Devices and Structures (PIDS), http://www.itrs.net/Links/2011ITRS/Home2011.htm, 2011.

- 5. C. S. Lent, P. D. Tougaw, W. Porod, and G. H. Bernstein, "Quantum cellular automata," Nanotechnology, vol. 4, no. 1, pp. 49–57, 1993.

- 6. S. Angizi, S. Sarmadi, S. Sayedsalehi, and K. Navi, "Design and evaluation of new majority gate-based RAM cell in quantum- dot cellular automata," Microelectron. Journal, no. 46, pp. 43–51, 2015.

- 7. M. R. Azghadi, O. Kavehie, and K. Navi, "A novel design for quantum-dot cellular automata cells and full adders," 2012, http://arxiv.org/abs/1204.2048.

- 8. D. Berzon and T. J. Fountain, "A memory design in QCAs using the SQUARES formalism,," in Proceedings of the Ninth Great Lakes Symposium on VLSI, pp. 166–169, Ann Arbor, MI, USA, March 1999.

- 9. K. Walus, A. Vetteth, G. Jullien, and V. Dimitrov, "Ram design using quantum-dot cellular automata," in Technical Proceedings of the 2003 Nanotechnology Conference and Trade Show, vol. 2, p. 160163, February 2003.

- 10. T. Lamjed, G. Ismail, L. Radhouane, and O. Bouraoui, "Efficient design of Bin DCT in quantum-dot cellular automata (QCA) technology," IET Image Processing, vol. 12, no. 6, pp. 1020–1030, 2016.

- 11. S. W. Kim and E. E. Swartzlander, "Parallel multipliers for quantum-dot cellular automata," in *Proceedings of the 2009 IEEE Nanotechnology Materials and Devices Conference*, pp. 68–72, Traverse City, MI, USA, June 2009.

- 12. S. W. Kim and E. E. Swartzlander, "Multipliers with coplanar crossings for quantum-dot cellular automata," in *Proceedings of the Conference on Nanotechnology*, pp. 953–957, Seoul, Korea, January 2010.